QR code

Producten

Neem contact met ons op

Telefoon

Fax

+86-579-87223657

E-mailen

Adres

Wangda Road, Ziyang Street, Wuyi County, Jinhua City, provincie Zhejiang, China

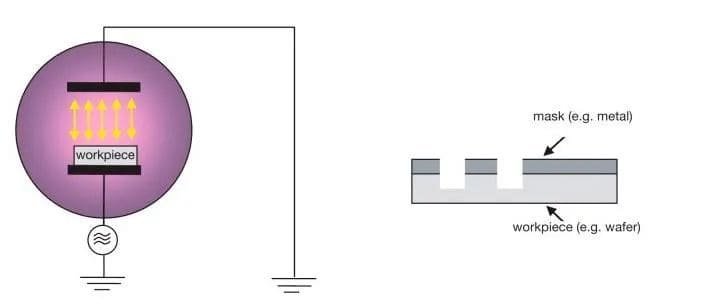

Etsentechnologie is een van de belangrijkste stappen in het halfgeleiderproductieproces, dat wordt gebruikt om specifieke materialen uit de wafer te verwijderen om een circuitpatroon te vormen. Tijdens het droge etsproces komen ingenieurs echter vaak problemen tegen zoals het laadeffect, het microgroefeffect en het oplaadeffect, die rechtstreeks van invloed zijn op de kwaliteit en prestaties van het eindproduct.

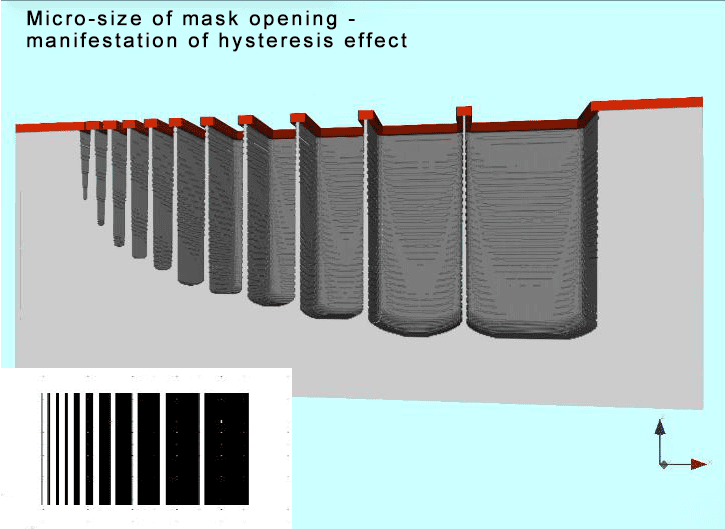

Het laadeffect verwijst naar het fenomeen dat wanneer het etsgebied toeneemt of de etsdiepte toeneemt tijdens het droge etsen, de etssnelheid afneemt of de etsen ongelijk zijn vanwege onvoldoende levering van reactief plasma. Dit effect is meestal gerelateerd aan de kenmerken van het etssysteem, zoals plasmadichtheid en uniformiteit, vacuüm graad, enz., En is wijd aanwezig in verschillende reactieve ionenetsen.

•Verbeter de plasmadichtheid en uniformiteit: Door het ontwerp van de plasmabron te optimaliseren, zoals het gebruik van efficiëntere RF-energie of magnetronsputtertechnologie, kan een hogere dichtheid en gelijkmatiger verdeeld plasma worden gegenereerd.

•Pas de samenstelling van het reactieve gas aan: Het toevoegen van een geschikte hoeveelheid hulpgas aan het reactieve gas kan de uniformiteit van het plasma verbeteren en de effectieve afvoer van etsbijproducten bevorderen.

•Optimaliseer het vacuümsysteem: Het verbeteren van de pompsnelheid en efficiëntie van de vacuümpomp kan de verblijftijd van etsbijproducten in de kamer helpen verminderen, waardoor het belastingseffect wordt verminderd.

•Ontwerp een redelijke lay -out voor fotolithografie: Bij het ontwerpen van de fotolithografische lay-out moet rekening worden gehouden met de dichtheid van het patroon om een te dichte opstelling in lokale gebieden te voorkomen en de impact van het belastingseffect te verminderen.

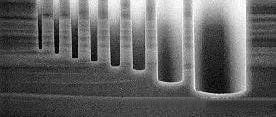

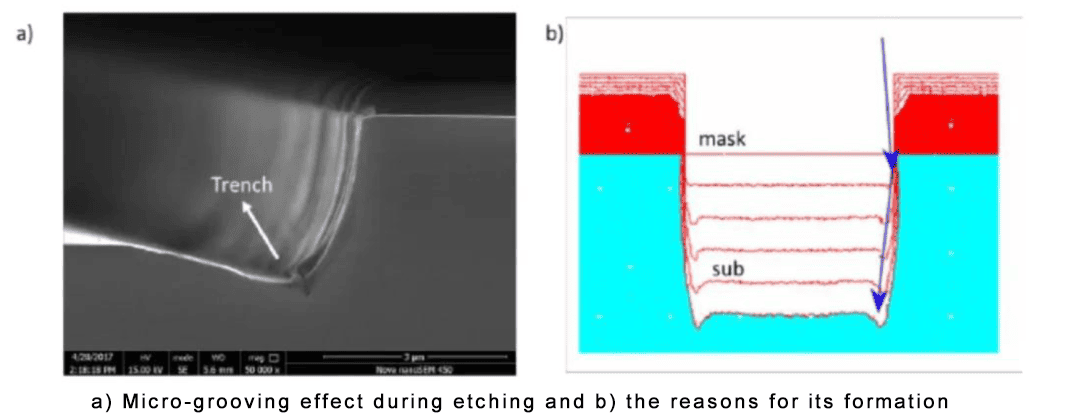

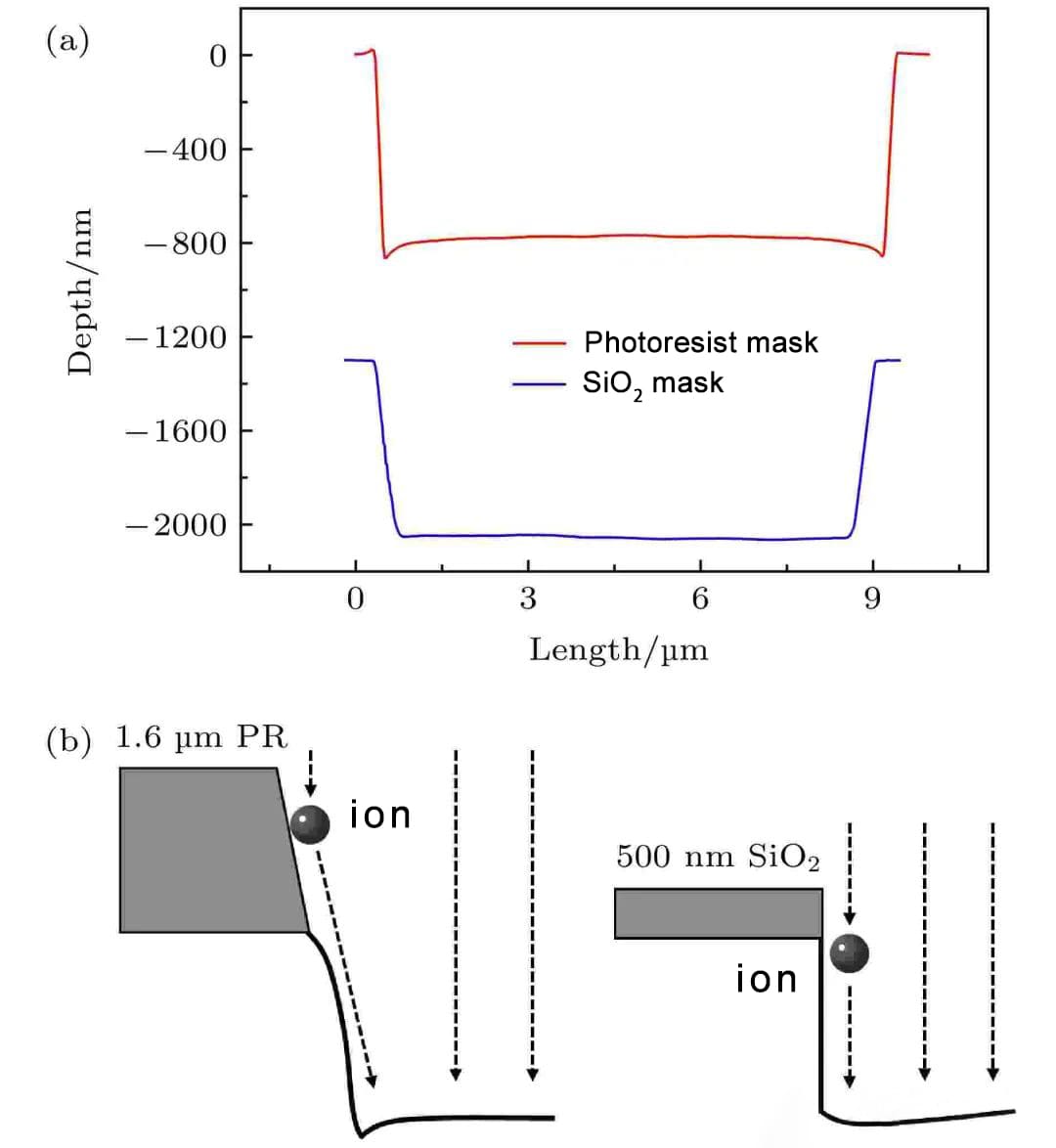

Het micro-trench-effect verwijst naar het fenomeen dat tijdens het etsproces, vanwege de energierijke deeltjes die het etsoppervlak bij een hellingshoek raken, de etssnelheid nabij de zijwand hoger is dan die in het centrale gebied, wat resulteert in niet -Verticale kamers aan de zijwand. Dit fenomeen is nauw verwant aan de hoek van de invallende deeltjes en de helling van de zijwand.

•Verhoog het RF-vermogen: Het correct verhogen van het RF -vermogen kan de energie van de invallende deeltjes vergroten, waardoor ze het doeloppervlak meer verticaal kunnen bombarderen, waardoor het etssnelheidsverschil van de zijwand wordt verminderd.

•Kies het rechter etsenmaskermateriaal: Sommige materialen zijn beter bestand tegen het oplaadeffect en verminderen het micro-trenching-effect dat wordt verergerd door de ophoping van negatieve lading op het masker.

•Optimaliseer de etsomstandigheden: Door parameters zoals temperatuur en druk tijdens het etsproces nauwkeurig aan te passen, kunnen de selectiviteit en uniformiteit van het etsen effectief worden gecontroleerd.

Het oplaadeffect wordt veroorzaakt door de isolerende eigenschappen van het etsmasker. Wanneer de elektronen in het plasma niet snel kunnen ontsnappen, zullen ze zich op het maskeroppervlak verzamelen en een lokaal elektrisch veld vormen, het pad van de invallende deeltjes verstoren en de anisotropie van het etsen beïnvloeden, vooral bij het etsen van fijne structuren.

• Selecteer geschikte etsmaskermaterialen: Sommige speciaal behandelde materialen of geleidende maskerlagen kunnen de aggregatie van elektronen effectief verminderen.

•Implementeer intermitterende ets: Door het etsproces periodiek te onderbreken en elektronen voldoende tijd te geven om te ontsnappen, kan het laadeffect aanzienlijk worden verminderd.

•Pas de etsomgeving aan: Het wijzigen van de gassamenstelling, druk en andere omstandigheden in de etsomgeving kunnen helpen de stabiliteit van het plasma te verbeteren en het optreden van het laadeffect te verminderen.

+86-579-87223657

Wangda Road, Ziyang Street, Wuyi County, Jinhua City, provincie Zhejiang, China

Copyright © 2024 WuYi TianYao Advanced Material Tech.Co.,Ltd. Alle rechten voorbehouden.

Links | Sitemap | RSS | XML | Privacybeleid |